全脑尺度的类脑计算需要支持千亿级神经元的实时互联与仿真计算的专用处理系统。单个甚至有限数量的计算芯片,难以支持如此大规模的神经元的集中计算,通常需要将海量的神经元切割分部到独立的专用处理芯片,由这些芯片构成大规模的分布式芯片处理网络,实现高能效的类脑计算专用处理系统。其中,实现规模化扩展的芯片级互联通信技术,是构建全脑尺度类脑计算系统的关键。区别于通用的芯片间通信技术,类脑专用的芯片通信技术的研发仍存在巨大挑战,需充分考虑和结合类脑计算中特有传播模式:1)连接模式多样且规模巨大;2)连接稀疏;3)神经元计算遵循异步触发的处理方式。

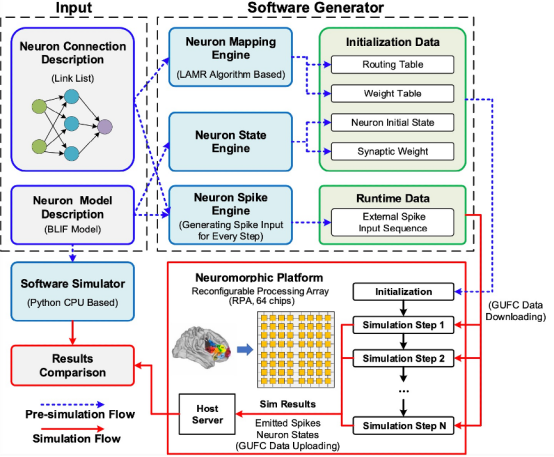

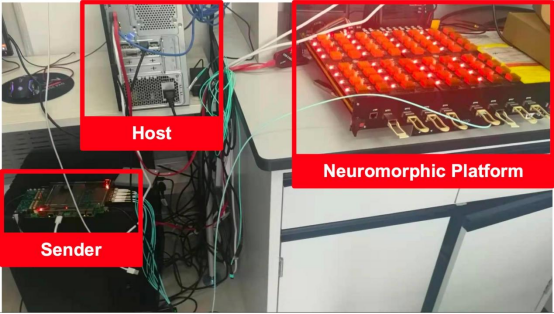

广东省智能科学与技术研究院类脑计算系统课题组一直致力于面向全脑尺度的类脑专用处理架构、芯片及系统的研究,近期在解决超大规模类脑计算芯片的连接问题上取得的重要突破,于3月1日在集成电路与系统领域Top期刊IEEE Transactions on Circuits and Systems I: Regular Papers上发表了题为“A Hybrid-Mode On-Chip Router for the Large-Scale FPGA-Based Neuromorphic Platform”的学术文章。论文分析了目前大规模类脑计算系统中存在的脉冲数据通信(spike communication)和非脉冲数据通信(non-spike communication)的两种基本通信模式,并针对超大规模类脑芯片互联中神经元脉冲传递的多模式、规模化、延时敏感的问题,提出了一种超低延时的可扩展、多模式的芯片网络互联架构(系统架构如图1所示),将可用于类脑芯片的互联扩展和超大规模类脑计算系统的构建。论文提出的类脑芯片间通信路由方案,已被应用部署到了团队自研的可编程计算阵列上,实现了单卡100 万个神经元和单机柜1亿神经元/1000亿神经突触的互联计算,构建的类脑计算系统如图2所示。根据评估,论文所提出的芯片间通信路由方案在多播模式下实现了 25ns 的路由解析延迟和 287ns 的芯片到芯片延迟,可在1ms的实时仿真精度下支撑千亿神经元规模的芯片计算网络构建,为全脑类脑计算系统的工程实现,提供了一条重要的技术途径。

广东省智能科学与技术研究院类脑计算系统研究组副研究员环宇翔博士为论文共同第一作者和共同通信作者,郑立荣和邹卓教授为论文共同通信作者。该项工作由智能院与复旦大学团队共同合作完成,工作得到国家基金委、广东省科技厅、上海市科委、以及智能院实验室建设项目等的支持。

图1. 论文提出的芯片网络互联架构在自研可编程计算阵列上的系统集成方案

图2.基于论文提出的类脑芯片网络互联架构的神经拟态计算系统

文章链接:https://ieeexplore.ieee.org/document/9723509