广东省智能科学与技术研究院类脑计算系统研究组一直致力于类脑专用处理架构、芯片及系统的研究,近期在解决硬件资源受限的边缘端神经网络处理上取得了新的突破,于2023年10月2日在集成电路与系统领域Top期刊IEEE Transactions on Circuits and Systems I: Regular Papers上发表了题为“ASLog: An Area-Efficient CNN Accelerator for Per-Channel Logarithmic Post-Training Quantization”的学术文章。文章针对神经网络算法在资源有限的物联网边缘设备上应用受限的问题,通过对神经网络模型和专用硬件的协同优化,提升了边缘端神经网络处理的存储和计算效率。

得益于算法的精简优化和神经网络专用加速器的发展,以深度学习为代表的人工智能应用正逐步从云端向终端迁移,智能计算将更加贴近数据的源头,物联网设备可就近提供边缘智能服务,满足行业数字化在敏捷连接、实时业务、数据优化、应用智能、安全与隐私保护等方面的关键需求。面向计算密集型和存储密集型的神经网络处理任务,相关专用加速器芯片的设计仍面临着挑战:一方面,神经网络算法要存储的数据量和处理的计算量远远大于其他常见的边缘端应用,使得冯·诺伊曼瓶颈问题在此应用场景中愈发严重;另一方面,边缘计算对硬件的成本、面积和功耗有着极为苛刻的要求,因而需在保证足够的性能前提下,尽量减小边缘神经网络加速器芯片的片上存储空间以降低芯片的面积、功耗和成本。

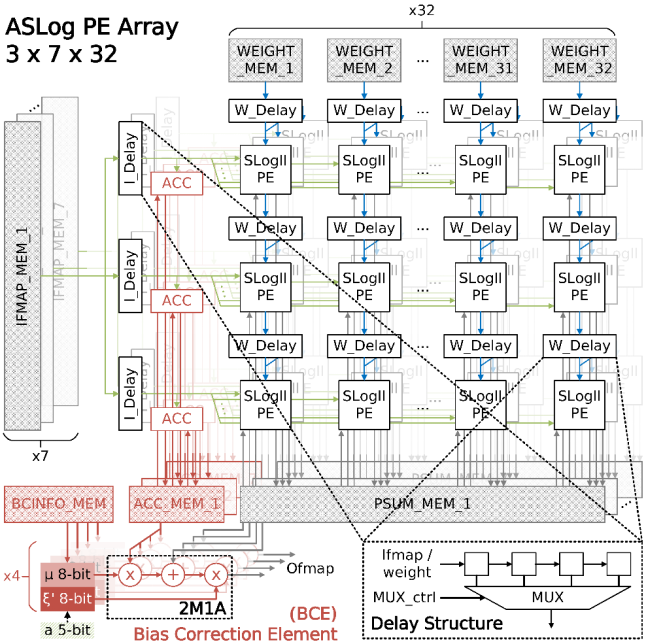

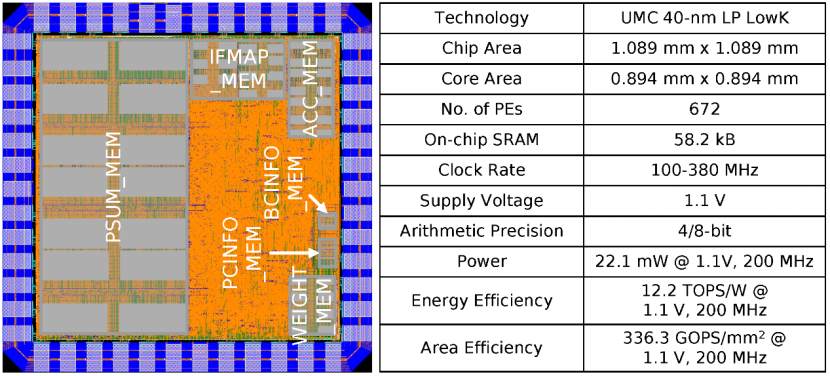

面向资源受限下的边缘端神经网络智能处理,本论文通过神经网络模型后训练量化(Post-Training Quantization, PTQ)算法与领域专用芯片的协同优化设计,实现了高能效、高存储效率、低功耗的专用神经网络加速器芯片。在算法层面,本论文设计实现了一种逐通道的后训练对数量化算法,不依赖原始数据集,不需要重训练或是微调操作,就能够以<2.5%的模型准确率损失实现>8倍的模型压缩效果,首次将后训练对数量化的极限优化至4-bit的数据精度。在硬件层面,本论文在类脉动阵列架构基础上,实现了在无乘法器基本运算单元、偏移修正计算单元、逐通道量化友好的数据流设计、多层级缓存结构、可重构专用计算单元阵列这五个层面上的细粒度优化。在UMC 40nm工艺下,该加速器芯片能够达到336.3 GOPS/mm2的面积效率(Area Efficiency),12.2 TOPS/W的能量效率(Power Efficiency),以及>500 Ops/Byte的算术运算强度(Operational Intensity)。

图1. 论文提出的后训练对数量化算法在专用硬件加速器上的部署方案

图2. 团队自研的面向逐通道后训练对数量化的神经网络加速器芯片

广东省智能科学与技术研究院类脑计算系统研究组徐佳唯博士为本文第一作者,研究员环宇翔博士为论文通信作者,郑立荣和邹卓教授为论文合著者。这项工作由智能院与复旦大学团队共同合作完成,工作得到国家基金委、广东省科技厅等项目的支持。

文章连接:

https://ieeexplore.ieee.org/document/10268644

微信扫一扫

关注该公众号